重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

重要提示:

请勿将账号共享给其他人使用,违者账号将被封禁!

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

更多“对于一个十位逐次通近式ADC电路,当时钟频率为1MHz时,其转换时间是多少?如果要求完成一次转换的时间小于10μs,试问时钟频率应选多大?”相关的问题

更多“对于一个十位逐次通近式ADC电路,当时钟频率为1MHz时,其转换时间是多少?如果要求完成一次转换的时间小于10μs,试问时钟频率应选多大?”相关的问题

第1题

第2题

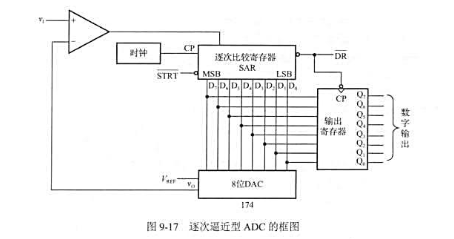

在图9-17所示逐次通近ADC电路中.名时钟频率为1MHz,输入的模拟电压为2.86V.试画出ADC输出v0的波形.

第4题

第5题

A.对于δ小于0情况,时钟偏差为负值降低了的抗竞争能力

B.当δ大于0时,时钟布线和数据通路方向一致,有利于时钟周期,却不利于保持时间

C.对于δ小于0情况,时钟布线和数据通路方向相反,不利于时钟周期,在一定程度上却有利于保持时间

D.时钟偏差具有改善电路性能的可能,电路可靠工作所要求的最小时钟周期随时钟偏差的增加而减小

第6题

第8题

第9题

钟信号CP的频率fc=10kHz,试问完成一次转换所需要的最长时间是多少?若已知计数器所计的数值N2=(369)10,基准电压UREF=±6V,则相应的输入模拟电压u1=?

警告:系统检测到您的账号存在安全风险

警告:系统检测到您的账号存在安全风险

为了保护您的账号安全,请在“上学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!